# Fault Injection Framework for Time-Triggered Systems

#### DISSERTATION

zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften (Dr.-Ing.)

Dissertation vorgelegt von:

Onwuchekwa, Daniel Lucky

eingereicht bei der Naturwissenschaftlich-Technischen Fakultät der Universität Siegen

Date of Oral Examination: 09. October 2020

#### Betreuer und erster Gutachter:

Prof. Dr. Roman Obermaisser, Universität Siegen

#### Zweiter Gutachter

Prof. Dr. Kristof Van Laerhoven, Universität Siegen

#### Prüfungskommission:

Prof. Dr. Roman Obermaisser

Prof. Dr. Kristof Van Laerhoven

Prof. Frank Gronwald

Prof. Malte Lochau

# Acknowledgement

I wrote this thesis during my employment at the department of Embedded Systems, University of Siegen. I thank Prof. Dr Roman Obermaisser for providing the opportunity for me to be a member of his team, and also for introducing me into the field of fault-tolerant and safety-critical systems. His valuable remarks and criticism advanced my scientific experience.

I would also like to thank my colleague, friend, and football teammate, Tobias Pieper. He played a considerable role that enabled my integration in Germany. He supported my settlement, taught me a lot about the German culture and introduced me to TSG Adler Dielfen football team, a common interest for us. I would also like to thank all my colleagues at the institute. Tobias, Hongie Fang and Maryam Palehvan have been an immense source of inspiration and a pool of knowledge which was beneficial during my work. I thank my colleague also Stefan Otterbach for ensuring that I get all the necessary tools required for the success of this work. I also thank Simon Meckel, Veit Wiese, Michael Schmidt, Hamidreza Ahmadian and Setareh Majidi for the pleasant atmosphere and harmony at work.

Special thanks go to my dearest wife Jennifer, who has been very helpful in providing constructive criticisms and exhibited patience on the way to reach my goal. She also provided the required emotional support to carry out my work. I also thank my kids, Giovanni and Gianna, for providing me with the necessary daily smiles and emotional support. I also thank my sisters Eberechi and Ezinne for their encouragement. I would also like to thank my in-laws for their presence and support in much needed time while I carried out my work. Finally, I would like to thank my friends Ugochukwu Osabiku, Oghneneochuko Obie, and Raymond Webilor for their support.

# Zusammenfassung

In dieser Dissertation wird eine Methodik zur Verifizierung und Validierung des Verhaltens von integrierten System vorgestellt, die auf zeitgesteuerten Ethernet-Netzwerken basieren. Der Determinismus und die ausreichende Bandbreite, die durch ein zeitgesteuertes Ethernet-Netzwerk bereitgestellt werden, ermöglichen die Konstruktion sicherheitskritischer Systeme in verschiedenen Bereichen wie Eisenbahn, Luftfahrt, Gesundheit und Automobil. Viele Anwendungen in diesen Bereichen stellen hohe Anforderungen an die Zuverlässigkeit. Deshalb sind Verifizierung und Validierung in den meisten Phasen des Entwicklungsprozesses sicherheitskritischer Systeme erforderlich.

Aufgrund der Komplexität von zeitgesteuerten Netzwerkprotokollen verwenden Entwickler meist formale Methoden und Simulationen als Verifikations- und Validierungstechniken. Allerdings verifizieren und validieren diese Methoden hauptsächlich bestimmte Funktionen der zeitgesteuerten Protokolle und nicht das Verhalten des integrierten Systems. Die Gründe dafür liegen in den Nachteilen dieser Ansätze. Die Modellierung komplexer Systeme führt bei der Benutzung formaler Methoden zu einer Explosion des Zustandsraums und Simulatoren modellieren bestimmte komplexe Funktionen nicht ausreichend. Des Weiteren erfordern Simulatoren eine zusätzliche Verifizierung durch ein physikalisches Netzwerk, um die Aussagekräftigkeit zu verbessern. Da die Evaluierung der physikalischen Realisierung von zeitgesteuerten Ethernet-Netzwerken zu den besten Ergebnissen führt, konzentriert sich diese Arbeit auf die Anwendung der Fehlerinjektion auf physikalische Geräte.

Diese Dissertation schlägt ein neuartiges und topologieunabhängiges Cut-Through-Fehlerinjektions-Framework vor, welches das integrierte Systemverhalten von zeitgesteuerten

Ethernet-Netzwerken auswerten kann. Sie bietet zudem eine Lösung für die Fehlererkennung in zeitgesteuerten Netzwerken während des Synchronisationsstarts, bevor eine

globale Zeit festgelegt wird. Darüber hinaus werden experimentelle Verfahren und Ergebnisse diskutiert, die die Verwendung des Fehlerinjektions-Frameworks für die Bewertung

einer Auswahl verschiedener Anwendungsfälle demonstrieren. Die hier durchgeführten

Experimente bestätigen, wie das neuartige Framework andere zeitgesteuerte Ethernet-

Frameworks übertrifft, indem es die kollektiven Anforderungen erfüllt. Hierzu gehören geringe Störanfälligkeit, Portabilität und die Abstraktion der Fehlerinjektionskomponente aus dem zu testenden Netzwerk.

## Abstract

This thesis presents a methodology and tool for verifying and validating the integrated system behaviour of time-triggered Ethernet networks. The determinism and sufficient bandwidth provided by time-triggered Ethernet network make it appealing for building safety-critical systems in different domains such as railway, aviation, health, and automobile. Many applications in these domains impose stringent dependability requirements. Therefore, verification and validation are often required at most stages of the development process when designing these systems.

Due to the complexity of time-triggered network protocols, design engineers mostly employ formal methods and simulations as the verification and validation techniques. However, these methods mainly verify and validate only certain functions of the time-triggered protocol and not the integrated system behaviour. The reasons stem from the downsides of these approaches. The formal method suffers from a state-space explosion when modelling complex systems, and simulators do not sufficiently model certain complex functionality. Simulators also require cross-verification from a physical network to gain better confidence. Since evaluating the physical realisation of time-triggered Ethernet networks results in the best confidence levels, this work then focuses on the use of fault injection on physical devices for this purpose.

This work proposes a novel and topology independent cut-through fault injection framework that can be used to evaluate the integrated system behaviour of time-triggered Ethernet networks. This work also describes a technique that can be used for failure detection in time-triggered networks during the synchronisation startup before the establishment of global time. It furthermore presents a discussion of experimental procedure(s) and results that demonstrate the use of the fault injection framework for the evaluation of a selection of different use cases. The Experiments carried out herein confirms how the novel fault injection framework surpasses other time-triggered Ethernet frameworks by satisfying a set of collective requirements which mainly include low-intrusiveness, portability, and the abstraction of fault injection component from the network under test.

# Contents

| Acknowledgement |                 |                   |                                             | Ι            |  |

|-----------------|-----------------|-------------------|---------------------------------------------|--------------|--|

| Zι              | Zusammenfassung |                   |                                             |              |  |

| $\mathbf{A}$    | bstra           | ct                |                                             | IV           |  |

| Ta              | able (          | of Con            | tents                                       | $\mathbf{V}$ |  |

| 1               | Intr            | $\mathbf{coduct}$ | ion                                         | 1            |  |

|                 | 1.1             |                   | xt and motivation                           | 1            |  |

|                 | 1.2             |                   | tives and contribution                      | 3            |  |

|                 | 1.3             | •                 | s structure                                 | 5            |  |

| <b>2</b>        | Bac             | kgrom             | nd Theory                                   | 7            |  |

| _               | 2.1             | _                 | ime systems                                 | 7            |  |

|                 | 2.2             |                   | adability of a system                       | 8            |  |

|                 |                 | 2.2.1             | Means to attain dependability in a system   | 8            |  |

|                 |                 | 2.2.2             | Threats to the dependability of a system    | 9            |  |

|                 |                 | 2.2.3             | Attributes of the dependability of a system | 10           |  |

|                 |                 | 2.2.4             | Redundancy                                  | 11           |  |

|                 |                 | 2.2.5             | Methods of dependability evaluation         | 12           |  |

|                 |                 | 2.2.6             | Safety                                      | 13           |  |

|                 |                 | 2.2.7             | Safety-criticality system                   | 13           |  |

|                 | 2.3             | Verific           | eation and validation                       | 14           |  |

|                 | 2.4             |                   | injection                                   | 14           |  |

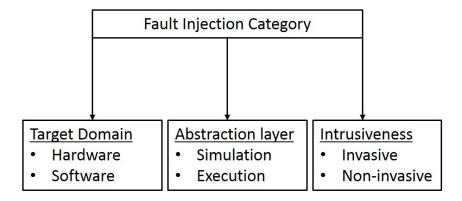

|                 |                 | 2.4.1             | Fault injection categorisation              | 15           |  |

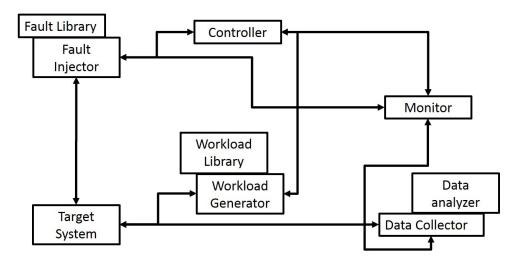

|                 |                 | 2.4.2             | Fault injection environment                 | 16           |  |

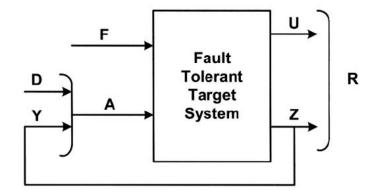

|                 |                 | 2.4.3             | Modelling a fault injection framework       | 17           |  |

|                 |                 | 2.4.4             | Types of fault injection                    | 19           |  |

|                 | 2.5             | Conce             | ept of deep learning                        | 21           |  |

|                 |                 | 2.5.1             | Machine learning                            | 21           |  |

|                 |                 | 2.5.2             | Deep learning                               | 22           |  |

| 3               | Tin             | ne-Trig           | gered Ethernet communication                | 26           |  |

|                 | 3.1             | Ether             | ,9                                          | 27           |  |

|                 |                 | 3.1.1             | Open system interconnection layers          | 27           |  |

|                 |                 | 3.1.2             | Key characteristics of Ethernet             | 28           |  |

|   |                                                             | 3.1.3 Components of Ethernet                                                                                                                                                                                                                                                                                                                                                                                                | 30                                                                                     |

|---|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|   |                                                             | 3.1.4 Absence of determinism in Ethernet                                                                                                                                                                                                                                                                                                                                                                                    | 31                                                                                     |

|   | 3.2                                                         | Time-triggered control                                                                                                                                                                                                                                                                                                                                                                                                      | 31                                                                                     |

|   |                                                             | 3.2.1 Clock and global time                                                                                                                                                                                                                                                                                                                                                                                                 | 32                                                                                     |

|   |                                                             | 3.2.2 Clock offset                                                                                                                                                                                                                                                                                                                                                                                                          | 33                                                                                     |

|   |                                                             | 3.2.3 Time-Triggered system                                                                                                                                                                                                                                                                                                                                                                                                 | 34                                                                                     |

|   | 3.3                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                             | 34                                                                                     |

|   |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                                                     |

|   |                                                             | 3.3.2 Fault tolerant clock synchronization                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                     |

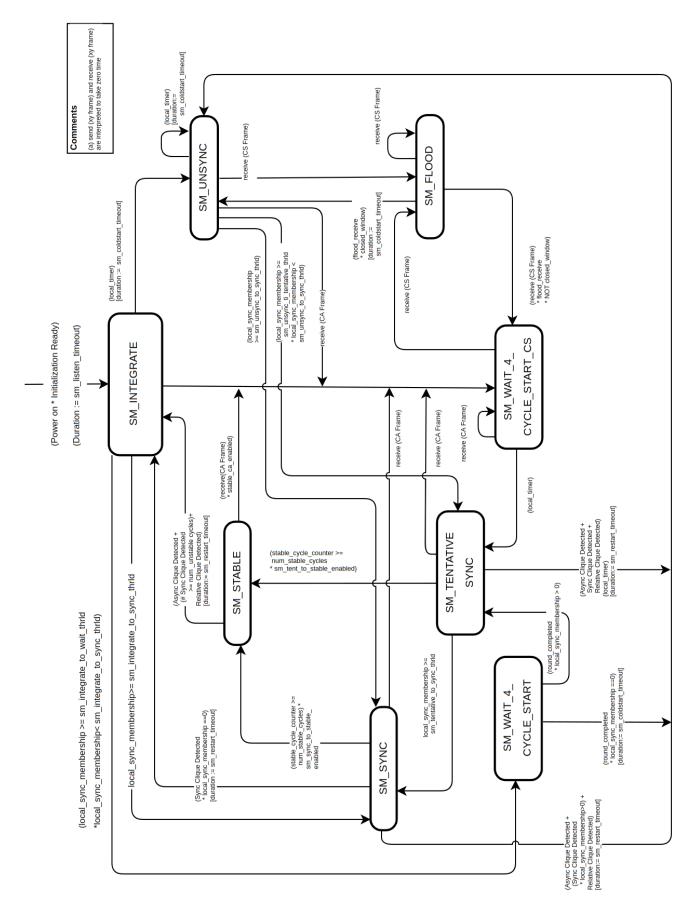

|   |                                                             | 3.3.3 TTEthernet startup and restart service                                                                                                                                                                                                                                                                                                                                                                                | 40                                                                                     |

|   | 3.4                                                         | Time sensitive networking                                                                                                                                                                                                                                                                                                                                                                                                   | 43                                                                                     |

|   |                                                             | 3.4.1 Background on precision time protocol and profile                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                                     |

|   |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                             | 49                                                                                     |

|   |                                                             | 3.4.3 Start-up time                                                                                                                                                                                                                                                                                                                                                                                                         | 50                                                                                     |

|   |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                        |

| 4 |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                             | 55                                                                                     |

|   | 4.1                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                                                                                     |

|   | 4.2                                                         | y .                                                                                                                                                                                                                                                                                                                                                                                                                         | 58                                                                                     |

|   | 4.3                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                                                     |

|   | 4.4                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                           | 63                                                                                     |

|   |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                                                                                     |

|   | 4 -                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                             | 68                                                                                     |

|   | 4.5                                                         | Summary of related works                                                                                                                                                                                                                                                                                                                                                                                                    | 69                                                                                     |

|   |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                        |

| 5 | Sys                                                         | tem Model of Fault Injection Framework                                                                                                                                                                                                                                                                                                                                                                                      | 72                                                                                     |

| 5 | <b>Sys</b> 5.1                                              | <b>J</b>                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>72</b><br>72                                                                        |

| 5 |                                                             | System model                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 5 |                                                             | System model                                                                                                                                                                                                                                                                                                                                                                                                                | 72                                                                                     |

| 5 | 5.1                                                         | System model                                                                                                                                                                                                                                                                                                                                                                                                                | 72<br>73                                                                               |

| 5 | 5.1                                                         | System model                                                                                                                                                                                                                                                                                                                                                                                                                | 72<br>73<br>74                                                                         |

| 5 | 5.1                                                         | System model                                                                                                                                                                                                                                                                                                                                                                                                                | 72<br>73<br>74<br>75                                                                   |

| 5 | 5.1                                                         | System model                                                                                                                                                                                                                                                                                                                                                                                                                | 72<br>73<br>74<br>75<br>78                                                             |

| 5 | 5.1                                                         | System model                                                                                                                                                                                                                                                                                                                                                                                                                | 72<br>73<br>74<br>75<br>78                                                             |

| 5 | 5.1                                                         | System model                                                                                                                                                                                                                                                                                                                                                                                                                | 72<br>73<br>74<br>75<br>78<br>80<br>81                                                 |

| 5 | 5.1                                                         | System model                                                                                                                                                                                                                                                                                                                                                                                                                | 72<br>73<br>74<br>75<br>78<br>80<br>81<br>81                                           |

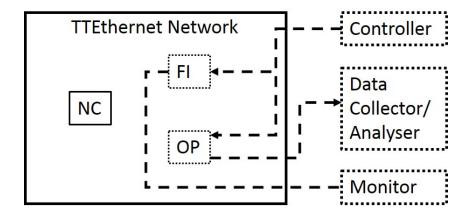

| 5 | <ul><li>5.1</li><li>5.2</li></ul>                           | System model 5.1.1 Fault hypothesis  TRAITOR in TTEthernet 5.2.1 Architectural overview of TRAITOR 5.2.2 Fault injector component 5.2.3 Observation probe 5.2.4 Data collector/analyser 5.2.5 Controller 5.2.6 Monitor  TSN fault injection framework                                                                                                                                                                       | 72<br>73<br>74<br>75<br>78<br>80<br>81<br>81<br>82                                     |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>               | System model 5.1.1 Fault hypothesis TRAITOR in TTEthernet 5.2.1 Architectural overview of TRAITOR 5.2.2 Fault injector component 5.2.3 Observation probe 5.2.4 Data collector/analyser 5.2.5 Controller 5.2.6 Monitor TSN fault injection framework FPGA block diagram design                                                                                                                                               | 72<br>73<br>74<br>75<br>78<br>80<br>81<br>82<br>83                                     |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>   | System model 5.1.1 Fault hypothesis TRAITOR in TTEthernet 5.2.1 Architectural overview of TRAITOR 5.2.2 Fault injector component 5.2.3 Observation probe 5.2.4 Data collector/analyser 5.2.5 Controller 5.2.6 Monitor TSN fault injection framework FPGA block diagram design Software design                                                                                                                               | 72<br>73<br>74<br>75<br>78<br>80<br>81<br>82<br>83<br>83                               |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                      | System model 5.1.1 Fault hypothesis TRAITOR in TTEthernet 5.2.1 Architectural overview of TRAITOR 5.2.2 Fault injector component 5.2.3 Observation probe 5.2.4 Data collector/analyser 5.2.5 Controller 5.2.6 Monitor TSN fault injection framework FPGA block diagram design Software design TRAITOR operation summary                                                                                                     | 72<br>73<br>74<br>75<br>80<br>81<br>82<br>83<br>83<br>84<br>86                         |

| 6 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>Imp               | System model  5.1.1 Fault hypothesis  TRAITOR in TTEthernet  5.2.1 Architectural overview of TRAITOR  5.2.2 Fault injector component  5.2.3 Observation probe  5.2.4 Data collector/analyser  5.2.5 Controller  5.2.6 Monitor  TSN fault injection framework  FPGA block diagram design  Software design  TRAITOR operation summary                                                                                         | 72<br>73<br>74<br>75<br>80<br>81<br>82<br>83<br>83<br>84<br>86                         |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Imp</b><br>6.1 | System model  5.1.1 Fault hypothesis  TRAITOR in TTEthernet  5.2.1 Architectural overview of TRAITOR  5.2.2 Fault injector component  5.2.3 Observation probe  5.2.4 Data collector/analyser  5.2.5 Controller  5.2.6 Monitor  TSN fault injection framework  FPGA block diagram design  Software design  TRAITOR operation summary  plementation  Fault injection component                                                | 72<br>73<br>74<br>75<br>80<br>81<br>82<br>83<br>83<br>84<br>86                         |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>Imp               | System model  5.1.1 Fault hypothesis  TRAITOR in TTEthernet  5.2.1 Architectural overview of TRAITOR  5.2.2 Fault injector component  5.2.3 Observation probe  5.2.4 Data collector/analyser  5.2.5 Controller  5.2.6 Monitor  TSN fault injection framework  FPGA block diagram design  Software design  TRAITOR operation summary  plementation  Fault injection component  Receiver logic                                | 72<br>73<br>74<br>75<br>78<br>80<br>81<br>82<br>83<br>84<br>86<br><b>88</b><br>88      |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Imp</b><br>6.1 | System model  5.1.1 Fault hypothesis  TRAITOR in TTEthernet  5.2.1 Architectural overview of TRAITOR  5.2.2 Fault injector component  5.2.3 Observation probe  5.2.4 Data collector/analyser  5.2.5 Controller  5.2.6 Monitor  TSN fault injection framework  FPGA block diagram design  Software design  TRAITOR operation summary  plementation  Fault injection component  Receiver logic  6.2.1 Retriever logic         | 72<br>73<br>74<br>75<br>78<br>81<br>82<br>83<br>83<br>84<br>86<br>88<br>89             |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Imp</b><br>6.1 | System model 5.1.1 Fault hypothesis TRAITOR in TTEthernet 5.2.1 Architectural overview of TRAITOR 5.2.2 Fault injector component 5.2.3 Observation probe 5.2.4 Data collector/analyser 5.2.5 Controller 5.2.6 Monitor TSN fault injection framework FPGA block diagram design Software design TRAITOR operation summary  Dlementation Fault injection component Receiver logic 6.2.1 Retriever logic 6.2.2 Corruption state | 72<br>73<br>74<br>75<br>80<br>81<br>82<br>83<br>84<br>86<br>88<br>89<br>90             |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Imp</b><br>6.1 | System model 5.1.1 Fault hypothesis TRAITOR in TTEthernet 5.2.1 Architectural overview of TRAITOR 5.2.2 Fault injector component 5.2.3 Observation probe 5.2.4 Data collector/analyser 5.2.5 Controller 5.2.6 Monitor TSN fault injection framework FPGA block diagram design Software design TRAITOR operation summary    Software design                                                                                  | 72<br>73<br>74<br>75<br>80<br>81<br>82<br>83<br>84<br>86<br>88<br>89<br>90<br>93<br>95 |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Imp</b><br>6.1 | System model 5.1.1 Fault hypothesis TRAITOR in TTEthernet 5.2.1 Architectural overview of TRAITOR 5.2.2 Fault injector component 5.2.3 Observation probe 5.2.4 Data collector/analyser 5.2.5 Controller 5.2.6 Monitor TSN fault injection framework FPGA block diagram design Software design TRAITOR operation summary    Software design                                                                                  | 72<br>73<br>74<br>75<br>80<br>81<br>82<br>83<br>84<br>86<br>88<br>89<br>90             |

|   |     | 6.2.6 Delay failure state                            |

|---|-----|------------------------------------------------------|

|   |     | 6.2.7 Link failure State                             |

|   |     | 6.2.8 Crash failure State                            |

|   |     | 6.2.9 Time synchronisation failure state             |

|   |     | 6.2.10 Stuck-At failure                              |

|   | 6.3 | TSN implementation                                   |

| 7 | Exp | periments, Results and Analysis 102                  |

|   | 7.1 | Experiment goals                                     |

|   | 7.2 | TTEthernet fault injection                           |

|   |     | 7.2.1 Usecase description and experiment setup       |

|   |     | 7.2.2 Results and discussions                        |

|   |     | 7.2.3 Conclusion                                     |

|   | 7.3 | Fault containment against babbling idiot failure     |

|   |     | 7.3.1 Usecase description and experiment Setup 109   |

|   |     | 7.3.2 Results and discussions                        |

|   |     | 7.3.3 Conclusion                                     |

|   | 7.4 | Deterministic communication in the railway domain    |

|   |     | 7.4.1 Fault assumption                               |

|   |     | 7.4.2 Usecase description                            |

|   |     | 7.4.3 Experiment setup                               |

|   |     | 7.4.4 Results and discussions                        |

|   |     | 7.4.5 Conclusion                                     |

|   | 7.5 | Failure detection in TSN startup using deep learning |

|   |     | 7.5.1 Usecase description and experiment setup       |

|   |     | 7.5.2 Results and discussions                        |

|   |     | 7.5.3 Conclusion                                     |

|   | 7.6 | Experiment summary                                   |

| 8 | Cor | nclusion and Perspective 134                         |

|   | 8.1 | Features and advantages of TRAITOR                   |

|   | 8.2 | Significance of TRAITOR                              |

|   | 8.3 | limitation                                           |

|   | 8.4 | Future work                                          |

# List of Figures

| Fig. | 1.1  | Thesis structure                                                                       | 6  |

|------|------|----------------------------------------------------------------------------------------|----|

| Fig. | 2.1  | The fundamental chain of dependability and security threats [Avizienis et al., 2004]   | 10 |

| Fig. | 2.2  | Fault Injection Category                                                               | 16 |

| Fig. |      | Basic components of a Fault injection framework                                        | 17 |

| 0    | 2.4  | Global framework depicting the applicability of FARM model, [Benso and Prinetto, 2003] | 18 |

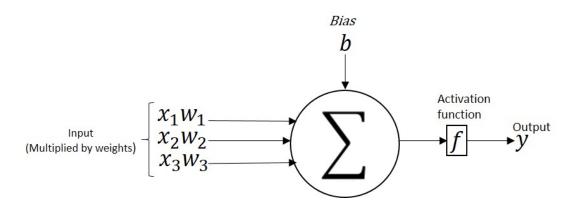

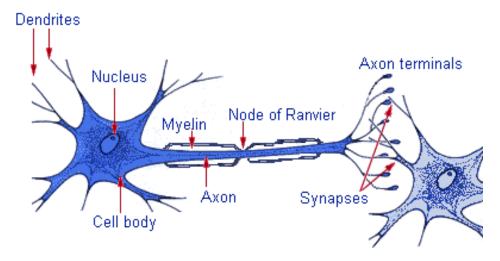

| Fig. | 2.5  | Model representation of a neural network                                               | 23 |

| Fig. |      | A network of two neurons [leavingbio, 2019]                                            | 24 |

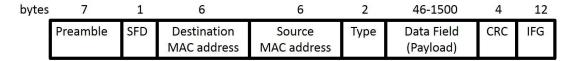

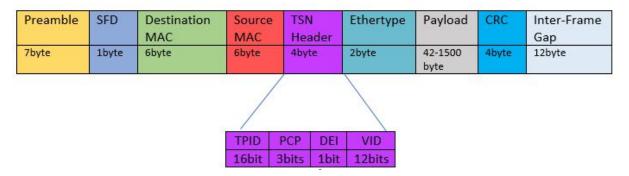

| Fig. | 3.1  | The Ethernet frame format                                                              | 28 |

| Fig. |      | An example structure of the Time-triggered network                                     | 32 |

| Fig. |      | The PCF frame format                                                                   | 37 |

| Fig. |      | Synchronization Master state machine                                                   | 42 |

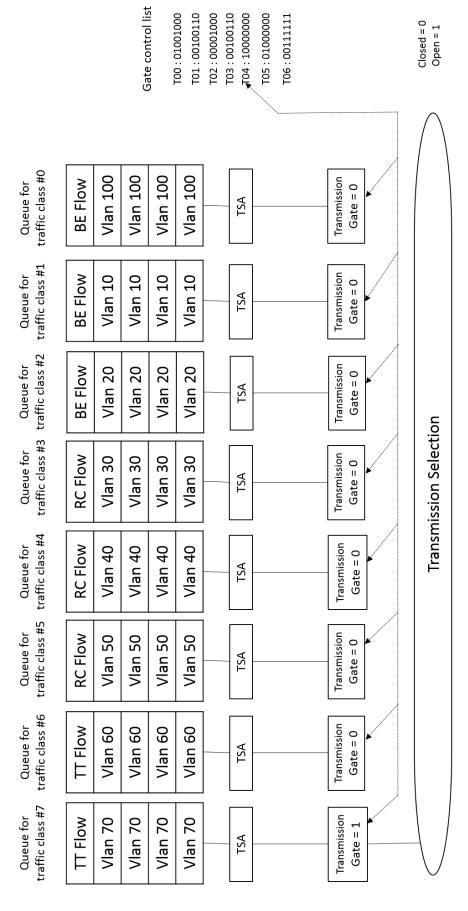

| Fig. |      | Illustration of IEEE 802.1Qbv transmission selection                                   | 46 |

| Fig. |      | PTP timing diagram for synchronization message exchange                                | 49 |

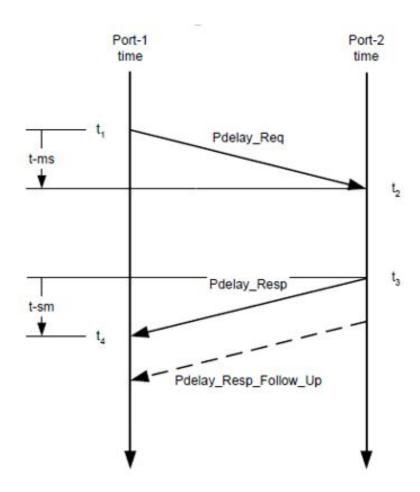

| Fig. |      | PTP link delay measurement                                                             | 50 |

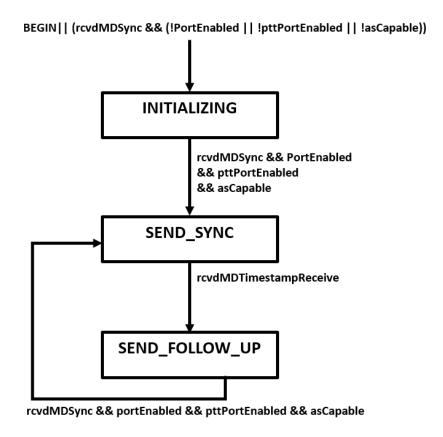

| Fig. |      | MDSyncSendSM state machine                                                             | 51 |

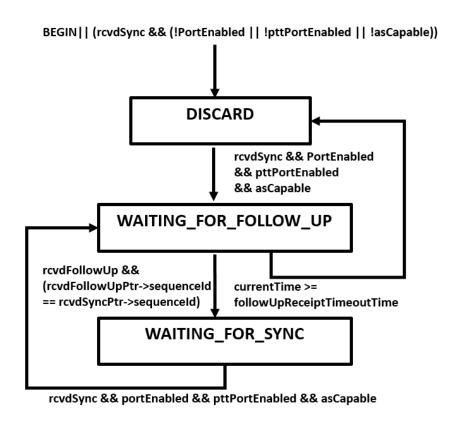

| Fig. |      | MDSyncReceiveSM state machine                                                          | 52 |

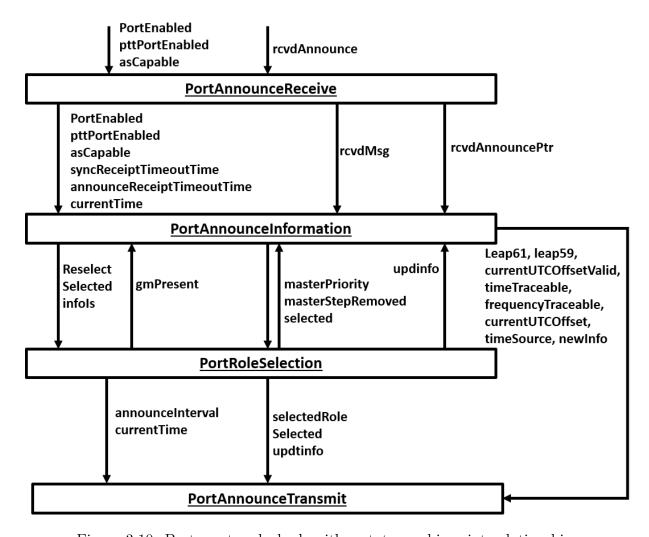

| Fig. |      | Best master clock algorithm state machines interelationships                           | 53 |

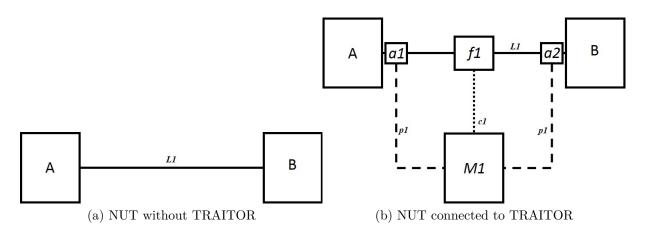

| Fig. | 5.1  | Overview of System Model                                                               | 73 |

| Fig. | 5.2  | System Architecture of the fault injection framework                                   | 75 |

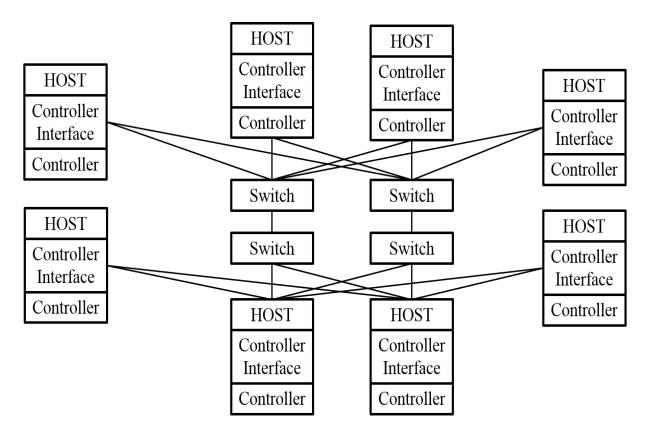

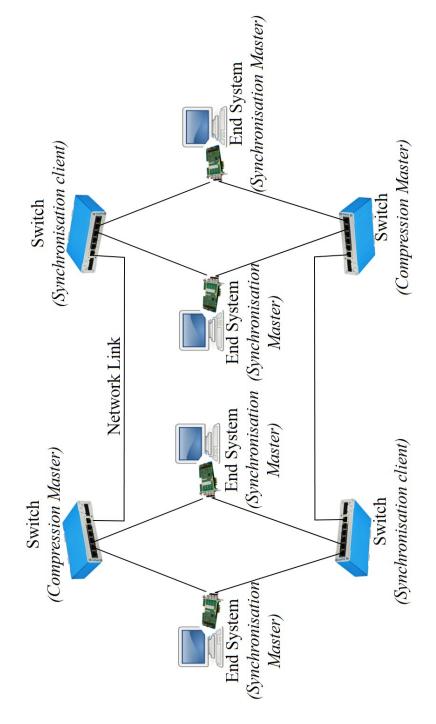

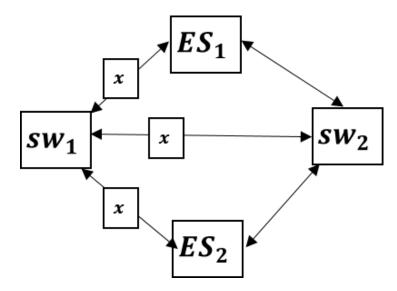

| Fig. | 5.3  | A typical redundant TTEthernet setup                                                   | 76 |

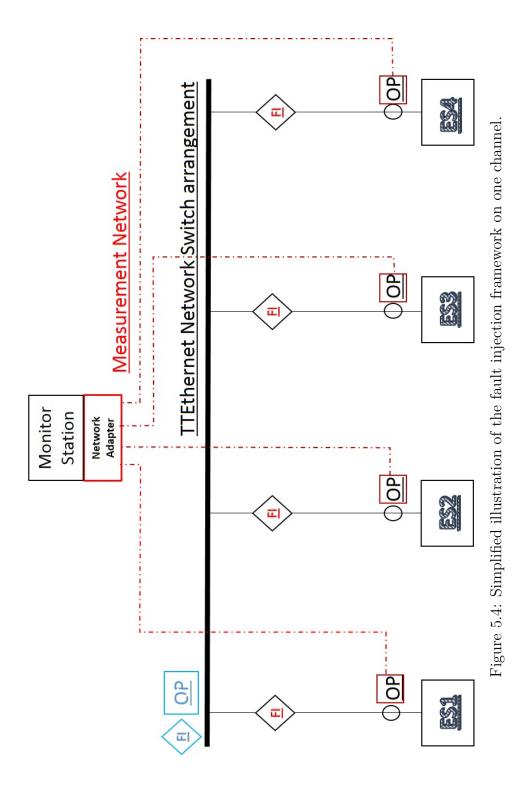

| Fig. | 5.4  | Simplified illustration of the fault injection framework on one channel.               | 77 |

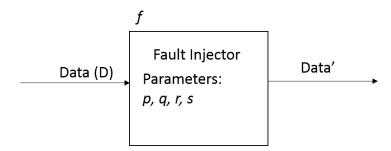

| _    |      | Fault Injector Model                                                                   | 78 |

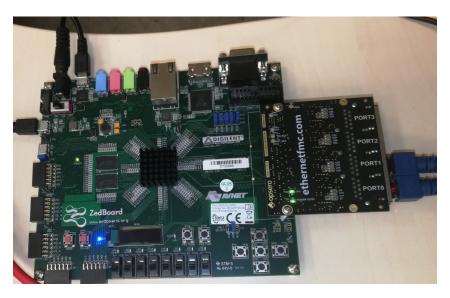

| Fig. | 5.6  | Zedboard with an Ethernet FMC addon                                                    | 79 |

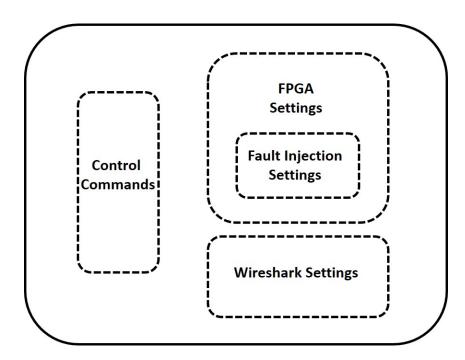

| Fig. | 5.7  | High-level Architecture of a Graphical User Interface                                  | 82 |

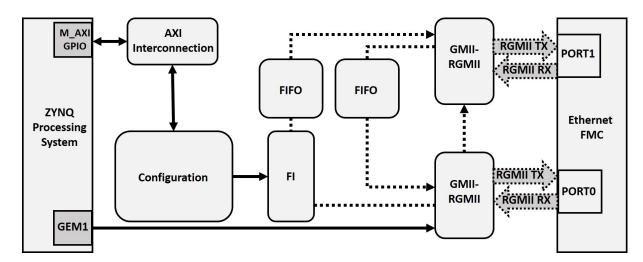

| _    |      | Block Diagram of FI design on FPGA                                                     | 84 |

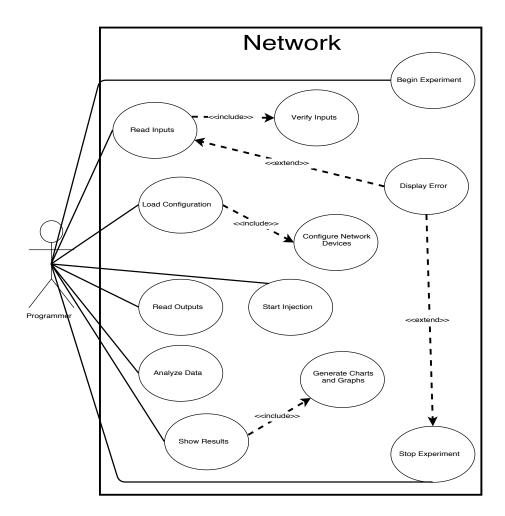

|      |      | Use case diagram of TRAITOR controller                                                 | 85 |

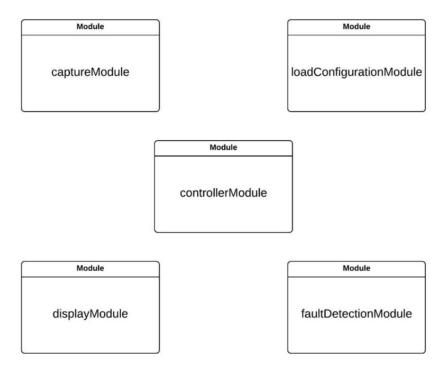

| Fig. | 5.10 | Modules of the controller software                                                     | 86 |

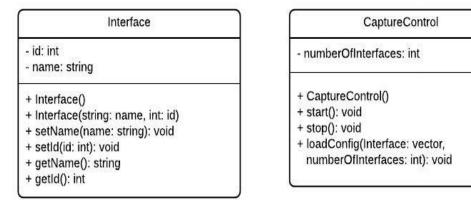

| Fig. | 5.11 | Class diagram of the captureModule                                                     | 87 |

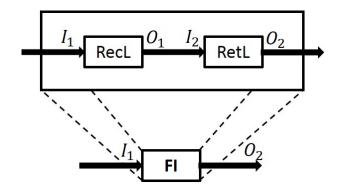

|      |      | Cascade composition of RecL and RetL                                                   | 89 |

| _    |      | RetL state machine                                                                     | 92 |

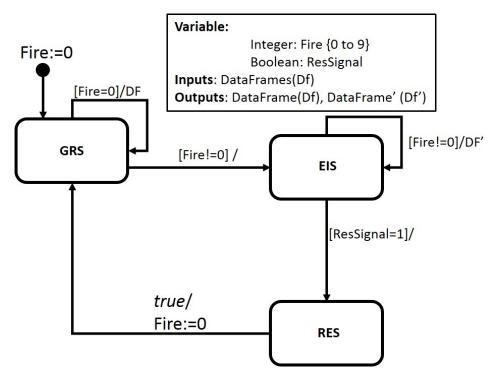

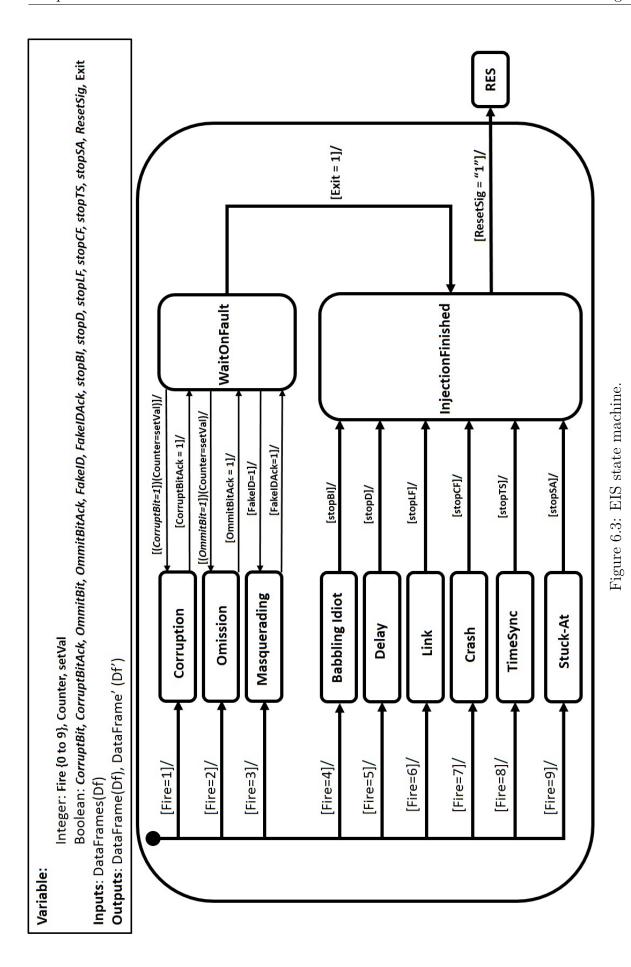

| Fig. | 6.3  | EIS state machine                                                                      | 94 |

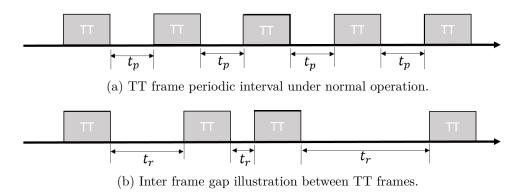

| Fig. | 6.4  | Inter frame gap illustration between TT frames                        | 97  |

|------|------|-----------------------------------------------------------------------|-----|

| Fig. | 6.5  | Example illustrating crash failure                                    | 100 |

|      |      | 802.1Q frame structure                                                |     |

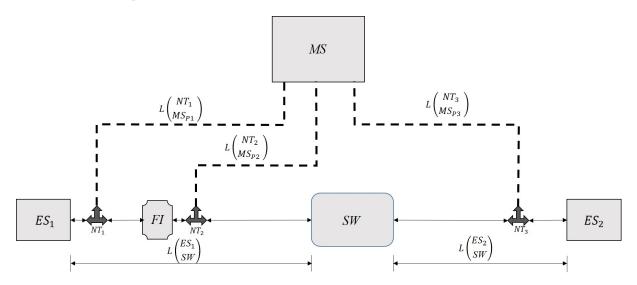

| Fig. | 7.1  | Single Hop Non-redundant network connected to a monitoring station    | 104 |

| _    |      |                                                                       | 106 |

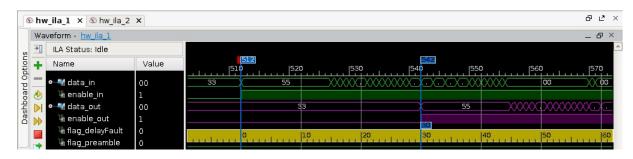

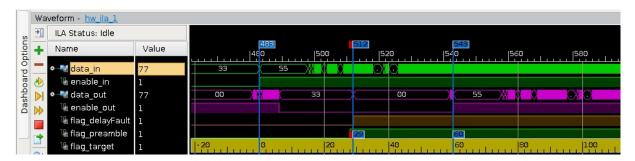

| _    |      | ILA illustration for delay fault of 1µs                               |     |

|      |      |                                                                       | 110 |

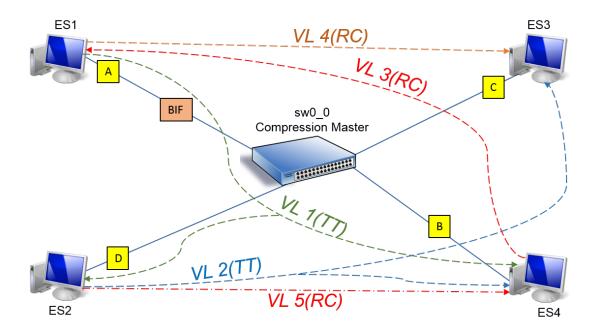

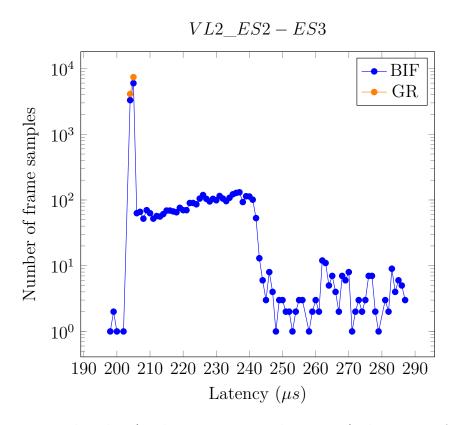

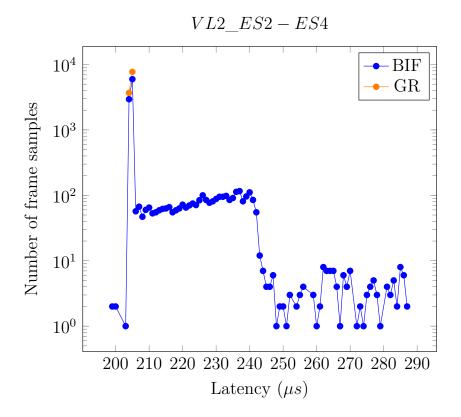

| Fig. | 7.5  | Virtual Link 2 (End system 2 to End system 3) observation for Jitter. | 113 |

| Fig. | 7.6  | Virtual Link 2 (End system 2 to End system 4) observation for Jitter. | 113 |

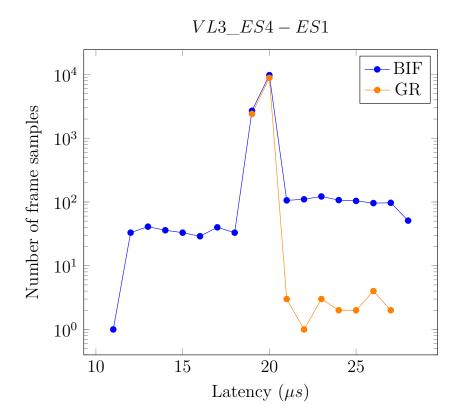

| Fig. | 7.7  | Virtual Link 3 (End system 4 to End system 1) observation for Jitter. | 114 |

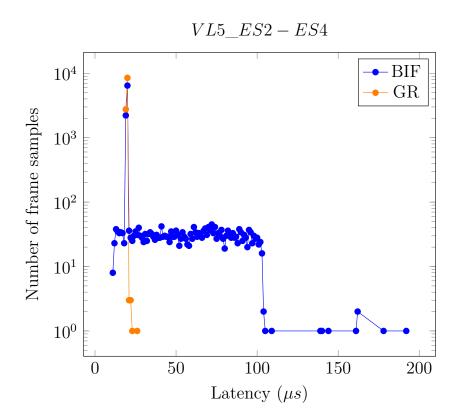

| Fig. | 7.8  | Virtual Link 5 (End system 2 to End system 4) observation for Jitter. | 115 |

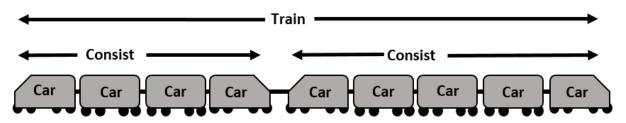

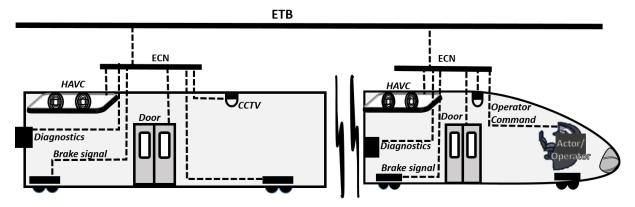

| Fig. | 7.9  | Train composition                                                     | 118 |

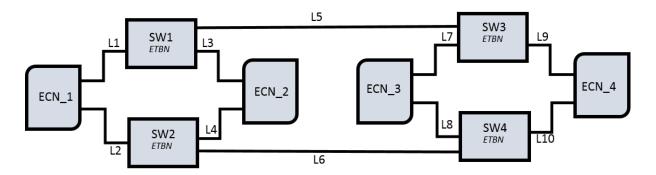

| Fig. | 7.10 | Train Consist network                                                 | 119 |

| Fig. | 7.11 | Train network setup based on TTEthernet                               | 121 |

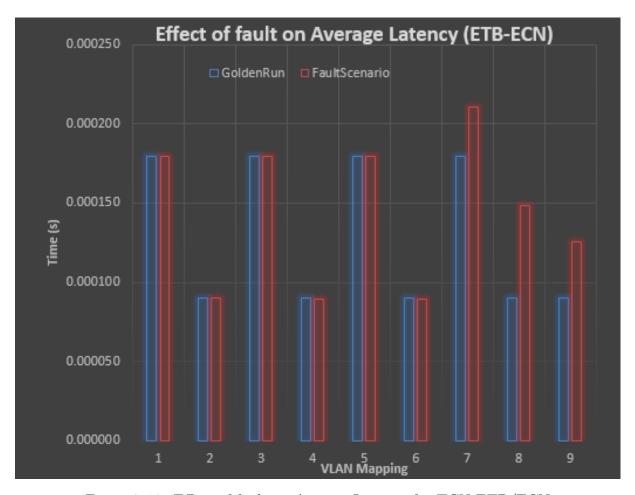

|      |      | Effect of fault on Average Latency for TCN-ETB/ECN                    |     |

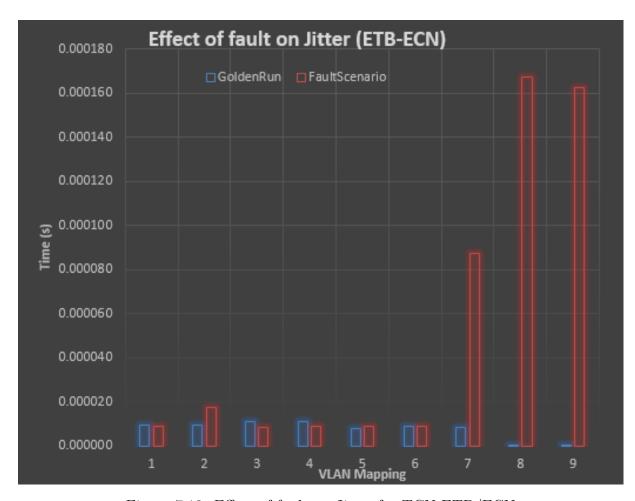

| Fig. | 7.13 | Effect of fault on Jitter for TCN-ETB/ECN                             | 124 |

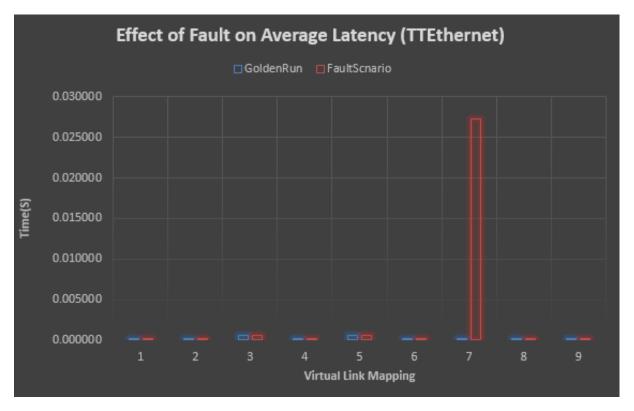

| Fig. | 7.14 | Effect of fault on Average Latency for TCN-TTEthernet                 | 126 |

|      |      | Effect of fault on Jitter for TCN-TTEthernet                          |     |

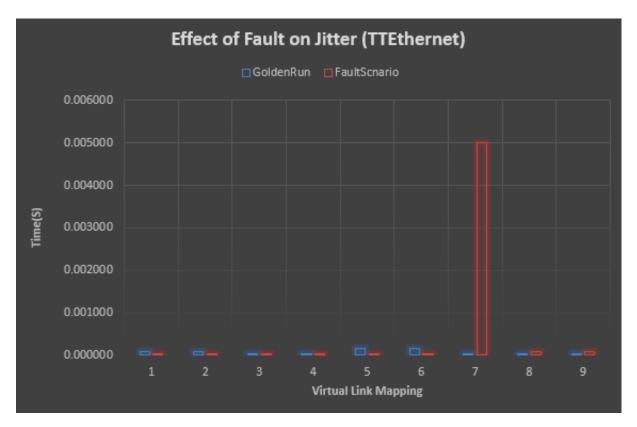

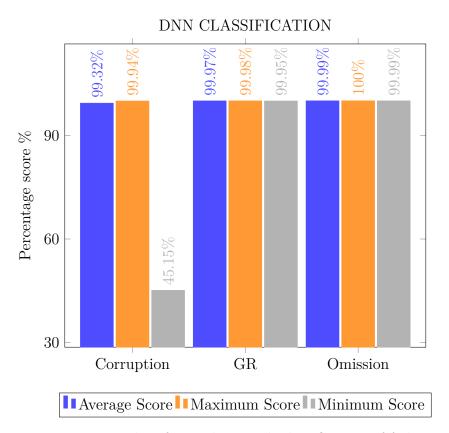

| Fig. | 7.16 | Experimental setup for data acquisition                               | 130 |

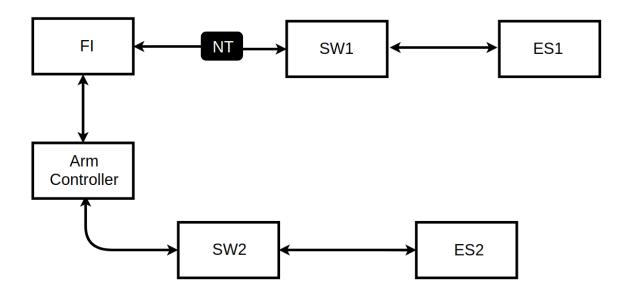

| _    |      | Results of neural network classification of failure                   |     |

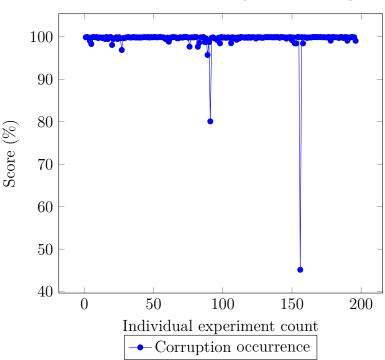

| Fig. | 7.18 | Results showing neural network score for corruption                   | 132 |

# List of Tables

| Tab. | 3.1 | Variant fault tolerant median for computing correction value 39                                                                                                |

|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tab. | 3.2 | Time-Sensitive Networking Standards                                                                                                                            |

| Tab. | 5.1 | Illustration on how the frame injection, frame Delay and Jamming can                                                                                           |

|      |     | be used to implement the different failure modes 80                                                                                                            |

| Tab. | 5.2 | Possible Fault locations                                                                                                                                       |

| Tab. | 5.3 | Relationship between number of bits supported by RGMII and network                                                                                             |

|      |     | speed                                                                                                                                                          |

| Tab. | 7.1 | Results of Corruption Failure (FER = 3) $\dots \dots \dots$    |

| Tab. | 7.2 | Results of Omission Failure (FER $= 3$ )                                                                                                                       |

| Tab. | 7.3 | Experimental Measurement - Golden run scenario and BIF injected                                                                                                |

|      |     | with a payload size(100B) and BAG (0.015s) $\dots \dots \dots$ |

| Tab. | 7.4 | VLAN profile for TCN based on ETB/ECN                                                                                                                          |

| Tab. | 7.5 | Virtual Link profile for TTEthernet use-case for Railway                                                                                                       |

| Tab. | 7.6 | Experiment results for TCN-ETB/ECN                                                                                                                             |

|      |     | Experiment results for TCN-TTEthernet                                                                                                                          |

| Tab. | 7.8 | Overview on the fulfilment of experimental goals                                                                                                               |

# Chapter 1

## Introduction

#### 1.1 Context and motivation

Today's world is currently experiencing the growing demand for embedded devices for applications in different sectors such as in aviation, health, railway and the military. The placement of these embedded devices is often done in a distributed fashion. As a consequence, computations are carried out locally on embedded devices that are placed in multiple locations. For example, let us consider a railway use case, where several Electronic Control Units (ECUs) are placed in different locations inside a railway vehicle. Each ECU is responsible for handling certain applications such as the Heating, Ventilation, and Air Conditioning (HVAC) system, door system, brake control, and entertainment system. These systems communicate with a central controller which issues control commands. This kind of system is a distributed system since each node performs local computations and also interacts with a central controller.

The communication infrastructure used to coordinate the interaction between devices that are located in different parts of the railway vehicle use-case and its controller is a distributed communication system. In the railway use-case, it can be observed that there is a mix of applications with different safety and real-time requirements. For instance, the door controller has higher safety and real-time constraint compared to the entertainment system. Therefore, embedded system designers tend to consider communication systems that satisfy these requirements. The current trend is towards time-triggered communication based on Ethernet that satisfies mixed-criticality safety requirements. The TTEthernet and the Time-Sensitive Networking (TSN) are examples of time-triggered communications that are based on Ethernet. These protocols satisfy mixed-criticality requirements by providing spatial and temporal separation, at the same time efficiently utilising avail-

able bandwidth, in addition to satisfying real-time constraints. This thesis was motivated by a project titled "SAFE architecture for Robust distributed Application Integration in roLling stock" (SAFE4RAIL) [Safe4RAIL, 2018] which developed concepts for the distributed communication platform, based on deterministic Ethernet communication. The distributed communication platform is named "Drive-by-Data" (DBD) in the SAFE4RAIL project.

The TTEthernet communication protocol has been used in the avionic industry and was standardised in 2010 [AS6802, 2011]. While the TSN is a group of standards in which all of the sub-standard is not yet completed as of today. Generally, time-triggered Ethernet networks provide the following advantages:

- Increased bandwidth for safety applications: Time-triggered networks based on Ethernet have the potential to provide more bandwidth compared to other protocols. For example, in the railway use case, Ethernet based communication provides more bandwidth compared to existing Train Communication Network (TCN), especially for the safety functions.

- Reduced complexity: The reduced complexity provided by time-triggered Ethernet networks can be illustrated with the railway example which consists of different protocols for high criticality applications and low safety-criticality applications. Currently, the Wire Train Bus/Multifunction Vehicle Bus (WTB/MVB) are used to implement safety functions while an Ethernet-based network named the Ethernet Train Backbone/Ethernet Consist network (ETB/ECN) is used for applications with large bandwidth requirements such as the entertainment systems. There is increased complexity in the maintenance and management of the mixed network. Hence the need for TTEthernet and TSN.

- Reduced Maintenance cost: There is a high cost incurred in maintaining multiple communication platforms as opposed to a single platform. Therefore, hosting all train applications on the same network would yield reduced cost for maintenance.

- Reduced weight: Time-triggered Ethernet networks host network traffic from applications with multiple safety-criticality levels on a single link. This feature avoids the traditional use of multiple wires for applications with different safety levels, hence the overall weight of all wires is reduced.

- Low latency and Jitters for message transmissions.

These benefits of time-triggered Ethernet networks are the reasons why it is a suitable candidate for railway, avionic, and automotive applications. Most verification and val-

idation activities of the time-triggered protocols carried out to this day focus on formal methods and simulations. These methods mainly verified and validated certain functions of the protocol and not the integrated system behaviour. Formal method suffers from a state-space explosion, and are therefore constrained to modelling only a limited set of behaviour. The approach of using simulators for verification and validation requires cross-verification from a physical network to gain better confidence. Certain complex functionality may not be sufficiently modelled in simulation, which poses a question of fidelity for the simulator. For this reason, verification of physical prototypes provides more confidence than formal methods and simulation. Dependability evaluation of a physical prototype can be achieved by fault injection. Verification and validation using physical fault injection for network protocols is not a new technique. However, a suitable framework that uses physical fault injection for time-triggered Ethernet networks such as TTEthernet and TSN to test for the variety of failures covered by major safety standards such as the IEC 61508 [IEC61508, 2010] remains unrealised. Considering the anticipated increase in the deployment of time-triggered Ethernet networks for different application, a verification and validation tool that covers a broad range of failures that can test the integrated services of time-triggered Ethernet networks including their synchronisation services is required.

In time-triggered networks, the correctness of the entire protocols depends on the synchronisation service. A major problem is that it is illogical to rely on the global time base before the completion of the startup process to implement diagnostic protocols to detect faulty network components. This is because the global time base is only established after the startup process. The early detection of failed components during startup would facilitate early activation of diagnostic services, and ensure that fault removal implementations are triggered earlier. Thus, there is the need to implement a solution to handle failures before the completion of the startup.

## 1.2 Objectives and contribution

This work aims at the research of fault injection techniques capable of verifying and validating the integrated system behaviour of time-triggered Ethernet networks such as TTEthernet and TSN, providing low intrusion and high confidence level. In addition, the work strives to implement a solution to failure detection during synchronisation startup before a global time base is established. In this work, a new fault injection framework named TRAITOR (cuT-thRough fAult InjecTiOn fRamework) for time-triggered Ethernet networks is proposed. TRAITOR is designed and implemented to induce the failures

listed in IEC 61508. This work enriches the sparse literature in the verification and validation of time-triggered Ethernet networks using physical fault injection. More insight into the integrated behaviour of the fault-tolerant implementation of time-triggered Ethernet networks during failure scenarios is desired. TRAITOR is aimed at validating time-triggered Ethernet network protocol implementations to assist in the final validation phase of systems designed on top of these protocols. TRAITOR is aimed at satisfying the following requirements:

- 1. The ability to target the physical execution of the distributed time-triggered protocol encompassing the combined software and hardware implementation. Time-triggered Ethernet networks require the combined operation of a distributed software and designated hardware components. Fault injection frameworks are often aimed at validating specific hardware components or software that are considered as a single unit. TRAITOR is required to target the protocol operation as a whole and not individual hardware or software components. Therefore, the required target domain is the network protocol.

- 2. TRAITOR is required to target the integrated services of time-triggered Ethernet networks, and the protocols of these networks comprise multiple services. For instance, TSN comprises several sub-protocols such as protocols for synchronisation, bridges and bridged networks, and frame replication and elimination. Likewise, TTEthernet comprises sub-services such as clock synchronisation, and startup service. TRAITOR is required to target the integrated behaviour of all services provided by time-triggered Ethernet networks.

- 3. TRAITOR is required to target the physical implementation of time-triggered Ethernet networks. The abstraction level of TRAITOR is not aimed at simulation or formal modelling but the physical implementation.

- 4. TRAITOR is required to be low intrusive. The addition of TRAITOR to the Network Under Test (NUT) should not affect its operation. TRAITOR should not introduce noticeable delays to the NUT that will affect its mode of operation.

- 5. TRAITOR is required to abstract the fault injector component from the NUT. Most physical fault injection frameworks require modification of the network components under test to achieve error injection, but herein TRAITOR realises the concept for a physical fault injection framework that does not require such modifications.

- 6. It is required for TRAITOR to be portable to multiple applications utilising timetriggered Ethernet networks as the underlying communication platform. Another dimension to the portability requirement is the applicability of TRAITOR to im-

Chapter 1.3 Thesis structure

plementations by multiple vendors. TRAITOR is required to be developed on the concept that different implementations of time-triggered Ethernet networks can be tested without the need to modify vendor-specific implementations or applications.

7. Finally, TRAITOR is required to deliver a technique to diagnose failures during the startup of synchronisation under different failure scenarios. The applicability of TRAITOR in data generation for fault diagnostics is explored. Herein, the use of TRAITOR to generate training data for a neural network is desired. Since time-triggered Ethernet networks are designed to be fault-tolerant systems with Safety Integrity Level 4 (SIL4) [IEC61508, 2010], waiting for a failure to occur in a SIL4 system is not feasible since the mean time to failure is very large. Therefore, TRAITOR is required to have the capability to generate the training and test data for different failure scenarios.

#### 1.3 Thesis structure

The structure of this thesis is shown in Figure 1.1. After the introduction presented in this chapter 1, the background theory is presented in chapter 2 to provide an understanding of the fundamental concepts used in this work. Chapter 3 describes the target networks, that is the TTEthernet and TSN, and provides the details of the characteristics of the respective networks and their prominent features. Chapter 4 provides a discussion about the related works in this field — the existing gaps in the state-of-art and how the proposed technique closes these gaps described in the requirements. Chapter 5 presents a discussion about the system model of TRAITOR. It provides a general overview of TRAITOR's design and operation. The detailed description of the implementation and algorithms of TRAITOR is presented in chapter 6. A series of experiments and evaluations are carried out in Chapter 7 to demonstrated the operation of TRAITOR, showing how it satisfies the design requirements, specifically the requirements which are outlined in Chapter 4. The sections 7.2, 7.3, 7.4, and 7.5 of Chapter 7 report the works carried out using TRAITOR in [Onwuchekwa et al., 2018], [Onwuchekwa and Obermaisser, 2018], [Onwuchekwa and Obermaisser, 2019 and [Onwuchekwa et al., 2020] respectively. The results of each test are also analysed in each of the mentioned sections. Finally, the conclusion of this work is presented in Chapter 8.

Chapter 1.3 Thesis structure

### -INTRODUCTION

**BACKGROUND THEORY**

TIME-TRIGGERED COMMUNICATION

-RELATED WORKS

- SYSTEM MODEL OF TRAITOR

- IMPLEMENTATION

EXPERIMENT, RESULTS, AND ANALYSIS

CONCLUSION AND PERSPECTIVE

Figure 1.1: Thesis structure

# Chapter 2

# **Background Theory**

This chapter discusses the basic concepts and terminologies used in this work. Firstly, the notion of a real-time system is presented in section 2.1. Section 2.2 introduces the concept of dependability of a system with an emphasis on the following: means to attain dependability, threats to dependability, attributes of dependability, the concept of redundancy, and the methods employed in dependability evaluation. Section 2.3 discusses verification and validation to make clear the distinctions between these concepts. Next section 2.4 explains in detail the idea of fault injection, fault injection categories, and fault injection environment. Section 2.5 then discusses deep learning and the associated terminologies used in this work.

### 2.1 Real-time systems

A system can be defined as a modelling concept which describes the mapping of a set of inputs to a set of outputs [Laplante, 2004]. When only the inputs and outputs of a system are of interest, without consideration of the internal operation of the system, then is the system referred to as a black-box. Conversely, the system is referred to as "white-box" when the interactions between the system's input(s) and its internal dynamics to give a corresponding output(s) are considered. The term system behaviour refers to the sequence of output in time of a system [Kopetz, 2011]. The intended behaviour of a real-time system according to the specification is known as the system's service. If the behaviour violates the specification, the behaviour represents a failure. A real-time system is one where the logical correctness of the system behaviour is tied both to the accuracy of the outputs and the physical time when these outputs are produced.

It can be argued that most systems are real-time; nevertheless, to make clear of the

degree of timeliness and consequence of failure, this work divides real-time systems into three classes. Depending on the severity of the consequence of not meeting a system time-constraint, a real-time system can be classified as hard, firm or soft. A hard real-time system is one in which the failure to satisfy the timing constraints can result in a catastrophe such as loss of life, severe damage to the environment and huge financial loss. The firm real-time describes a system in which missed deadlines result in the generation of unusable or inaccurate system outputs. The distinction between the hard and firm real-time system is that missed deadlines in the firm real-time system do not result in a catastrophic consequence, even though the service delivered becomes useless in the event of a missed deadline. The soft real-time is used to describe a system which still produces useful output after a missed deadline.

## 2.2 dependability of a system

The work in [Laprie, 1992] described the dependability of a system as the measures taken to justify the reasons for trusting the services delivered by the system. In more recent times, a more refined definition in [Avizienis et al., 2004] described dependability of a system as the ability to avoid service failures that are more frequent and more severe than acceptable. This work adopts the concepts of dependability presented in [Avizienis et al., 2004], which attempted to establish a consensus of concepts for dependability.

#### 2.2.1 Means to attain dependability in a system

The means to attain dependability in a system can be classified into four categories namely, fault prevention, fault tolerance, fault removal and fault forecasting. A system that provides verified fault preventive mechanisms and fault-tolerance services can be considered to deliver trusted services. Fault prevention and fault tolerance aim to deliver trusted services while fault removal and fault forecasting aim to reach confidence in that ability.

Fault prevention is the means to prevent the occurrence or introduction of faults. Fault prevention is implemented during the development phase of system design. Some examples of prevention strategies for software and hardware can include the use of a modular structure for programming and information hiding, and the use of design rules.

Fault tolerance is the means to deliver correct service in the presence of faults. It is carried out in dependable systems using fault detection, fault containment, fault localisation, fault recovery and fault masking mechanisms [Barry, 1989]. Fault detection identifies whether

there is a fault present in a system. Fault containment is the process of isolating the fault to prevent error propagation through the system. Fault localisation involves the determination of where a fault occurs. Fault recovery mechanisms transform a system ladened with error into a state without errors. Fault masking achieves fault tolerance by hiding faults, such that it prevents a system from introducing errors into its information structure.

Fault removal is the means to reduce the number or severity of faults. It can be considered all through a system lifecycle, from development to deployment. During the development phase, fault removal involves three steps, namely, verification, diagnosis and correction. Every embedded system must be designed to meet certain requirements, and these requirements are called *properties* or *specifications*. Verification is the process of checking whether systems adhere to the specified property. Verification is discussed in more details in section 2.3. Diagnosis and correction of faults are carried out when the system fails its verification. Fault removal for an already deployed system is usually in the form of corrective or preventive maintenance.

Fault forecasting is the technique used to predict the occurrence of a fault in a system, to isolate, remove or circumvent these faults. This is achieved by evaluating the system behaviour either qualitatively (ordinal evaluation) or quantitatively (probabilistic evaluation).

#### 2.2.2 Threats to the dependability of a system

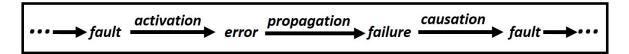

The threats to a dependable system are faults, errors, and failures [Arlat et al., 1993]. A fault is a physical defect, imperfection, or flaw that occurs in a hardware or software component of a system. Precisely, a fault can be defined as the adjudged or hypothesised cause of an error. An error is the part of a system's total state that may lead to a failure [Avizienis et al., 2004]. When a fault results in an error, it is said to be "active" otherwise it is "dormant". Errors can be propagated from one system sub-state to another, eventually resulting in the system's failure, except if it is tolerated or contained. Service failure is the event that occurs when the error is perceived by the users or external systems [Natella et al., 2016]. The deviation of a system from providing the correct service is termed service failure. The service failure may manifest in different ways known as service failure modes. The "chain of threats" shown in figure 1, as cited in [Avizienis et al., 2004] illustrates the relationship between fault, error and failure. If a fault produces an error when activated, this error can be propagated from one system component to another if not contained, which can then result in the system's failure. In the case of a complex system where the failure is localised on a certain component, the failed component has the potential to

cause another fault, thereby prolonging the chain of events. The taxonomy of faults given in [Avizienis et al., 2004] classified faults into three major partially overlapping groupings, namely, development faults, physical faults, and interaction faults. The development faults are the faults that occur during the development process of a system. Physical faults are all the possible faults that affect hardware component of a system. Interaction faults are all the faults that originate externally to the system.

Figure 2.1: The fundamental chain of dependability and security threats [Avizienis et al., 2004]

Apart from the service failure, failures can also be classified into two additional classes; the development failures, and dependability and security failures. Development faults may be introduced into a system during the development phase by its environment, human developer, and development tools. These faults may lead to partial or development failures or may remain undetected in the development phase and manifest in the use phase. Failures that occur during the development phase are termed as development failures. Similarly, it is to be expected that various kinds of faults can also affect a system during it's use phase causing unacceptably degraded performance or even total service failure. A dependability and security specification is agreed upon to states goals for dependability attributes (see next section 2.2.3 for dependability attributes). Thus a dependability and security failure occurs in the use phase when the given system suffers service failures more frequently or severely than acceptable.

#### 2.2.3 Attributes of the dependability of a system

The dependability concept is integrative, it encompasses the attributes: availability, reliability, safety, integrity, and maintainability. Availability can be defined as the readiness of a system to provide correct service. The reliability of a system is the probability that a system will continue to provide the specified service until time t, given that the system was operational at  $t = t_o$  [Kopetz, 2011]. Safety is reliability regarding malign (critical) failure modes. Safety is further explained in Subsection 2.2.6. Integrity describes the absence of improper system alterations. Maintainability is used to describe the ability of a system to undergo modification and repair.

#### 2.2.4 Redundancy

Redundancy is an essential requirement in fault tolerance [Verma et al., 2011]. Redundancy is the introduction of additional support of information, time or resources to a system, to give the system fault-tolerance capabilities and prevent failure. Redundancy can be attained by replicating hardware, software, information or by addition of extra time to perform a certain function.

#### Hardware redundancy

Hardware redundancy is the addition of extra hardware for the purpose of detecting or tolerating faults. Hardware redundancy can be achieved using three techniques, namely, **passive**, **active** and **hybrid** methods [Verma et al., 2011]. In *passive* technique, fault masking is achieved by replicating hardware and exploiting voting or median of the module output to determine the correct output, such as in Triple Modular Redundancy (TMR) or N-Modular redundancy. The *active* technique achieves fault tolerance by detecting the faults and then performing a function to remove the faulty hardware. Detection is achieved using a comparison function. The *hybrid* technique combines the passive and active method.

#### Information redundancy

Information redundancy occurs when redundancy is introduced into the transmitted data or into the memory of a system. Techniques to verify the correctness of message transmission are exploited, such as checksums, cyclic codes, and duplicate codes used to store additional information.

#### Time redundacy

Time redundancy is achieved by the repetition of computations targeted at detecting transient faults. A computation can be performed multiple times, or a message retransmitted multiple times to detect transient faults. However, extra time is required and thus, can pose challenges in applications with stringent timing requirements. Nevertheless, it is useful when extra time can be provided, for instance, using high-speed devices and in situations where additional hardware cannot be used for redundancy.

#### Software redundancy

Software redundancy is the addition of extra software for the purpose of detecting or tolerating faults. Software redundancy can be implemented in different forms. For instance, a complete replica of a program can be implemented. The downside is that software flaws are often a result of incorrect design. Therefore, given a flawed specification, different software implementations based on this specification will fail in a correlated manner. However, techniques such as consistency checks, capability checks, and N-version programming are used to implement software redundancy. The N-version programming uses the comparisons of designs, code and results of multiple versions of the same software to detect design flaws. Consistency checks use prior knowledge about output to detect certain errors. Capability checks are performed to verify that a system possesses the capability expected.

#### 2.2.5 Methods of dependability evaluation

There are several methods of evaluating the dependability of a system. A classification based on the intent of these methods is given in [Benso and Prinetto, 2003]. These methods include dependability evaluation by analysis, field experience, and testing. In dependability evaluation by analysis, the analysis of a process or product can be applied at different stages of a product development lifecycle. For example, in the 'concept phase' of product design, some applied techniques include performing comparative studies, Preliminary Hazard Identification and Analysis (PHIA), risk analysis, risk evaluation, and consequence analysis. In later design phases, when the system architecture is available, other techniques applied include reliability block diagram, Fault Tree Analysis (FTA), Failure Mode and Effect Analysis (FMEA), and simulations. However, dependability evaluation by analysis can be affected by high complexities, unavailability of certain information, and invalid assumptions.

After a system has gone into service, its dependability can also be evaluated. This evaluation is known as evaluation by field experience. However, field experience is not feasible when the dependability requirement is very high. For example, the relationship between the observation time T, desired confidence ( $\gamma$ ) and the hazardous failure rate ( $\lambda$ ) are shown in equation 2.1. The reaching of 95% confidence for a Safety Integrity Level 4 (SIL4) system,  $\lambda = 10^{-9}$ , requires an infeasible observation time. This spells out the challenges with evaluation by field experience.

$$T = -\ln(\gamma)^* 1/\lambda \tag{2.1}$$

Dependability evaluation by fault injection is deployed when direct evidence by testing is a feasible way to provide the required evidence for validation. Fault injection is discussed in section 2.4 in more detail. However, it is important to note that dependability evaluation

by fault injection reduces the observation time needed to verify/validate a system.

#### 2.2.6 Safety

There are respective boundary conditions for safety in different fields. For instance, in the automotive industry, safety is often discussed as the property of a system that describes the probability of correct operation without critical failures that could cause harm to people or the environment. Automotive producers stretch this definition to mean that the system should cause no accident by any means. This is because even if there is no harm to people, drivers could still cause an accident. Therefore, producers make efforts to prevent any possible occurrence of accidents [Leveson, 2012].

In the area of risk management, safety can be defined as freedom from unacceptable risk. In this context, the risk must be tolerable to be safe [IEC61508, 2010]. However, [Committee et al., 1999] gives a general definition of system safety as the application of engineering and management principles, criteria, and techniques to optimise all aspects of protection within the constraints of operational effectiveness, time and cost throughout all phases of the system life cycle.

#### 2.2.7 Safety-criticality system

A safety-criticality system is a system whose failure can result to harm impacted onto the physical world (people, property or environment). Safety-criticality systems exist across several domains. In the medical field, some examples of safety-criticality systems include the insulin pump hardware, heart pacemaker, defibrillator machines, and medical imaging devices (e.g. X-ray). Similar examples of safety-criticality systems in the automotive industry include systems such as the airbag, braking, seat belt, power steering and battery management systems. In the aviation industry, similar examples include the engine control, air traffic control and radio navigation system. The vast majority of these safety-criticality applications require real-time guarantees, which describes the property of a system to deliver its services to meet a specified deadline.